Southbridge (computing)

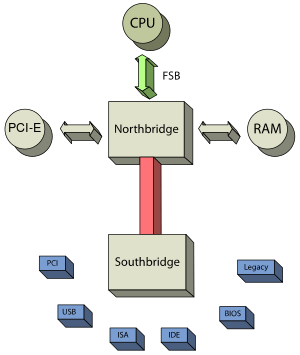

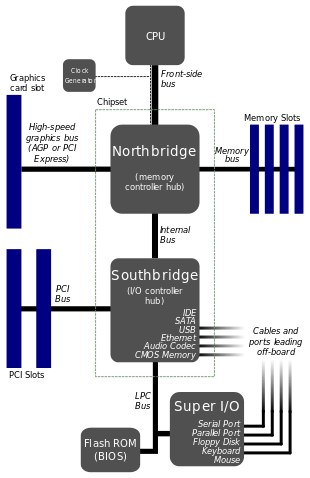

The southbridge is one of the two chips in the core logic chipset on a personal computer (PC) motherboard, the other being the northbridge. The southbridge typically implements the slower capabilities of the motherboard in a northbridge/southbridge chipset computer architecture. In systems with Intel chipsets, the southbridge is named I/O Controller Hub (ICH), while AMD has named its southbridge Fusion Controller Hub (FCH) since the introduction of its Fusion APUs.

The southbridge can usually be distinguished from the northbridge by not being directly connected to the CPU. Rather, the northbridge ties the southbridge to the CPU. Through the use of controller integrated channel circuitry, the northbridge can directly link signals from the I/O units to the CPU for data control and access.

Current status

Due to the push for system-on-a-chip (SoC) processors, modern devices increasingly have the northbridge integrated into the CPU die itself; examples are Intel's Sandy Bridge[1] and AMD's Fusion processors,[2] both released in 2011. The southbridge became redundant and it was replaced by the Platform Controller Hub (PCH) architecture introduced with the Intel 5 Series chipset in 2008. All southbridge features and remaining I/O functions are managed by the PCH which is directly connected to the CPU via the Direct Media Interface (DMI).[3]

Overview

A southbridge chipset handles all of a computer's I/O functions, such as USB, audio, serial, the system BIOS, the ISA bus, the interrupt controller and the IDE channels.[4] Different combinations of Southbridge and Northbridge chips are possible,[5] but these two kinds of chips must be designed to work together;[6][7] there is no industry-wide standard for interoperability between different core logic chipset designs. Traditionally, the interface between a northbridge and southbridge was the PCI bus. The main bridging interfaces used now are DMI (Intel) and UMI (AMD).

Etymology

The name is derived from representing the architecture in the fashion of a map and was first described as such with the introduction of the PCI Local Bus Architecture in 1991. At Intel, the authors of the PCI specification viewed the PCI local bus as being at the very centre of the PC platform architecture (i.e., at the Equator).

The northbridge extends to the north of the PCI bus backbone in support of CPU, memory/cache, and other performance-critical capabilities. Likewise the southbridge extends to the south of the PCI bus backbone and bridges to less performance-critical I/O capabilities such as the disk interface, audio, etc.

The CPU is located at the top of the map at due north. The CPU is connected to the chipset via a fast bridge (the northbridge) located north of other system devices as drawn. The northbridge is connected to the rest of the chipset via a slow bridge (the southbridge) located south of other system devices as drawn.

Although the current PC platform architecture has replaced the PCI bus backbone with faster I/O backbones, the bridge naming convention remains.

Functionality

The functionality found in a contemporary southbridge includes:[7]

- PCI bus. The PCI bus support includes the traditional PCI specification, but may also include support for PCI-X and PCI Express (PCIe).

- ISA bus or LPC bridge. ISA support remains an integrated part of the modern southbridge, though ISA slots are no longer provided on more recent motherboards. The LPC bridge provides a data and control path to the super I/O (the normal attachment for the keyboard, mouse, parallel port, serial port, IR port, and floppy controller) and FWH (firmware hub which provides access to BIOS flash storage).

- SPI bus. The SPI bus is a simple serial bus mostly used for firmware (e.g., BIOS) flash storage access.

- SMBus. The SMBus is used to communicate with other devices on the motherboard (e.g., system temperature sensors, fan controllers, SPDs).

- DMA controller. The DMA controller allows ISA or LPC devices direct access to main memory without needing help from the CPU.

- Interrupt controllers such as 8259A and/or I/O APIC. The interrupt controller provides a mechanism for attached devices to get attention from the CPU.

- Mass storage controllers such as PATA and/or SATA. This typically allows direct attachment of system hard drives.

- Real-time clock. The real time clock provides a persistent time account.

- Power management (APM and ACPI). The APM or ACPI functions provide methods and signaling to allow the computer to sleep or shut down to save power.

- Nonvolatile BIOS memory. The system CMOS (BIOS configuration memory), assisted by battery supplemental power, creates a limited non-volatile storage area for system configuration data.

- AC'97 or Intel High Definition Audio sound interface.

- Out-of-band management controller such as a BMC or HECI.

Optionally, a southbridge also includes support for Ethernet, RAID, USB, audio codec, and FireWire. Where support is provided for non-USB keyboard, mouse, and serial ports, a machine normally does so through a device referred to as a Super I/O; still more rarely, a southbridge may directly support the keyboard, mouse, and serial ports.

See also

- Integrated memory controller (IMC)

- Memory Controller Hub (MCH)

References

- ↑ Vatto, Kristian. "Why Ivy Bridge is still Quad-core?". Anandtech. Retrieved September 27, 2015.

- ↑ Stokes, Jon. "With Fusion, AMD's devils are in the details". Arstechnica. Retrieved September 27, 2015.

- ↑ "Mobile Intel HM57 Express Chipset". Intel. Retrieved 2014-04-21.

- ↑ "What is Southbridge?", Webopedia Computer Dictionary (word definition).

- ↑ Chipset: Northbridge and Southbridge, Rigacci.

- ↑ What is northbridge, southbridge, how northbridge, southbridge works, Edu soft max.

- 1 2 What is a chipset?, UK: Misco.

External links

- "Motherboards & Core-Logic Chipsets: The Deep Stuff > What the North Bridge and South Bridge Do". InformIT. Retrieved November 18, 2010.